STMicroelectronics has unveiled new microcontrollers (MCUs) targeting the coming electrified drivetrains and domain-oriented,over-the-airupdateable systems that are the foundation of the next generation of EVs. As the vehicles generate, process, and transfer large data flows, especially to support the next generation of EVs, ST’s new Stellar P automotive MCUs are the industry’s first qualifiable devices for model year 2024 vehicles to integrate the new CAN-XL in-car communication standard. This technology enables the new vehicle platforms to handle growing data flows so the car can operate at peak performance.

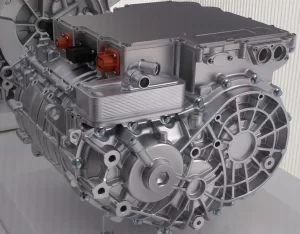

The new Stellar P series of automotive MCUs offers qualifiable devices that combine advanced actuation capabilities with powerful function integration. Stellar P devices target the new drivetrain trends for electric vehicles and domain-oriented architectures, for the best real-time performance and energy management.

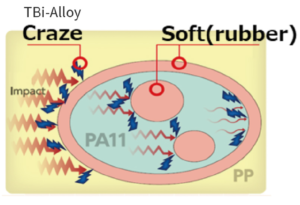

Manufactured in ST’s own wafer fabs using power-efficient 28nm FD-SOI technology, the Stellar P6 embeds up to 20 Mbytes of Phase Change (non-volatile) Memory (PCM). Developed and tested according to stringent automotive requirements for high-temperature operation, radiation hardening, and data retention, ST’s PCM also delivers faster access time through single-bit overwrite, a feature unavailable in Flash. In addition, over-the-air updates with no downtime leverage a game-changing mechanism that saves memory by dynamically allocating memory space to the new downloaded software image until it is validated. This happens while the rest of the memory continues to execute the running application in real-time.

ST’s Stellar P6 MCUs contain up to six Arm® Cortex® R52 processor cores, some operating in lockstep and some in split-lock mode to provide failsafe redundancy. These enable the new devices to deliver high performance, real-time determinism, and upgradeability for next-generation automotive drivetrains, electrification solutions, and domain-oriented systems. Stellar P6 manages hardware virtualization (sandboxing) using the Cortex-R52 features and firewalls to resource access. This simplifies the development and integration of multiple-source software on the same chip while ensuring safe isolation and performance.

State-of-the-art safety measures at all levels of the architecture ensure the most efficient implementation of ISO 26262 ASIL-D functions. In addition, the FD-SOI technology inherently offers a quasi-immunity to radiation and provides superior protection against system unavailability while ensuring compliance with the most stringent safety standards.

A fast hardware security module (HSM), extended with cryptographic engines operating in lockstep, supports secure ASIL D functions and enables enhanced EVITA full security capability. It also provides high-speed security cryptographic services and safe network authentication to further protect manufacturer firmware as well as end-users’ data.